Source: Content by Semiconductor Core News (ID: MooreNews) IEEE

Last week, at the IEEE Electronic Components and Technology Conference (ECTC), researchers pushed for the latest advancements in a technology that is crucial for cutting-edge processors and memory. This technology is called hybrid bonding, which stacks two or more chips together in the same package. Although the traditional transistor shrinking speed that once defined Moore's Law has slowed down overall, chip manufacturers can still increase the number of transistors in processors and memory.

A research team from major chip manufacturers and universities showcased various hard won improvements, including application materials Imec、 The research results of companies such as Intel and Sony may lead to record breaking levels of connection density between 3D stacked chips, with approximately 7 million connections per square millimeter of silicon wafer.

Intel's Yi Shi told ECTC engineers that all these connections are necessary due to the new properties of semiconductor advancements. As explained by Ann Kelleher, General Manager of Intel Technology Development, to IEEE Spectrum in 2022, Moore's Law is now governed by a concept called System Technology Collaborative Optimization (STCO). In STCO, the functions of the chip (such as cache, input/output, and logic) are separated and manufactured using the best manufacturing techniques for each function.

Then, hybrid bonding and other advanced packaging technologies can reassemble them, making them work like a whole silicon wafer. But this can only be achieved with high-density connections, which can transfer bits between silicon wafers with almost no delay or energy consumption.

Hybrid key merging is not currently the only advanced packaging technology, but it provides the highest density of vertical connections. Chris Scanlan, Senior Vice President of Technology at Besi, stated that hybrid bonding dominates ECTC, accounting for approximately one-fifth of the research showcased, and the company's tools are the driving force behind multiple breakthroughs.

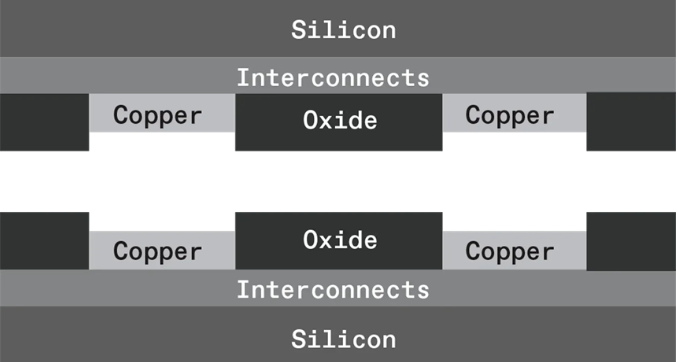

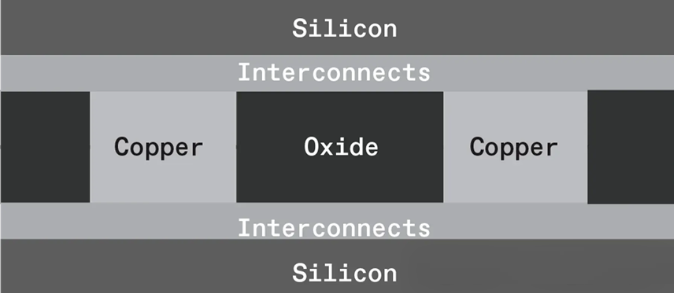

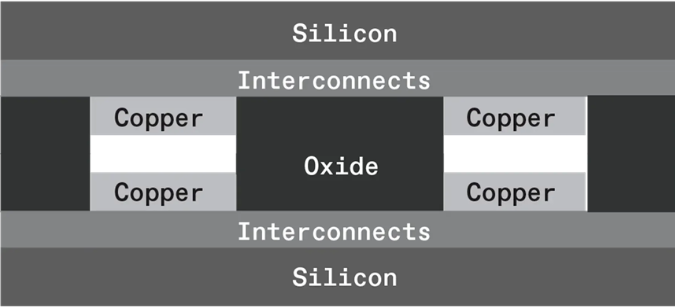

In hybrid bonding, copper pads are constructed on the top surface of each chip. Copper is surrounded by an insulating layer (usually silicon oxide), and the solder pad itself is slightly recessed into the surface of the insulating layer. After chemical modification of the oxide, the two chips are pressed face-to-face to align the recessed pads with each other. Then slowly heat the interlayer to expand the copper to the gap and connect the two chips.

Hybrid bonding can be used to connect a single chip to a wafer filled with larger chips, or to bond two wafers filled with chips of the same size together. The latter is more mature than the former, partly due to its application in camera chips. For example, Imec reported some of the densest wafer to wafer (WoW) bonding ever, with a bonding distance (or spacing) of only 400 nanometers. The same research center has achieved a 2-micron spacing in the chip to wafer (CoW) scenario. The connection spacing of commercial chips today is about 9 microns

With equipment, alignment between wafers is easier than alignment between chips and wafers. Most microelectronic processes are performed on [whole] wafers, "said Jean Charles Souriau, head of integration and packaging science at the French research institution CEA Leti. However, chip to wafer (or chip to wafer) technology shines in high-end processors such as AMD's Epyc series, which are used to assemble computing cores and cache memory in their advanced CPUs and AI accelerators.

In order to promote a tighter spacing between the two schemes, researchers focused on making the surface slightly flatter, allowing the bonded wafers to stick better together and reducing the time and complexity of the entire process. Doing all of this well may ultimately mean a revolution in the way chip design is done.

In the report, we observed the study of wafer to wafer (WoW) with the closest spacing (500 nanometers to 360 nanometers), all of which focused heavily on one thing: flatness. To bond two wafers together with a precision of 100 nanometers, the entire wafer must be almost completely flat. If it bends or twists, the entire material part cannot be connected.

Flattening wafers is a process called chemical mechanical planarization (CMP). It is usually the key to chip manufacturing, especially the process part of producing the interconnect layer above the transistor.

Souriau stated, "CMP is a key parameter for mixed bonding that we must control. ”The results presented at ECTC this week take CMP to a new level, not only flattening the entire wafer, but also reducing the roundness of the insulation layer between copper pads to the nanometer level to ensure better connections.

Other studies focus on ensuring that these flat components can be firmly bonded together by testing different surface materials, such as using silicon nitride instead of silicon oxide, or using different schemes to chemically activate the surface. Initially, when wafers or chips are pressed together, they are fixed together through relatively weak hydrogen bonds, with the focus on ensuring that everything remains in place between bonding and subsequent steps. Then, the bonded wafers and chips will slowly heat up (this process is called annealing) to form stronger chemical bonds. How strong these keys are - and how to figure them out - is a subject of extensive research at ECTC.

The final bonding strength also comes in part from the copper connection. The annealing step extends copper to the gap, forming a conductive bridge. Samsung's Seung Ho Hahn explained that controlling the size of the gap is key. If the gap is too large, copper cannot be connected. If the gap is too small, it will push the wafer away. This is a nanoscale problem, and Hahn reported research on a new chemical process that aims to achieve this by etching off one atomic layer of copper at a time.

The quality of the connection is also important. Even after copper expansion, most schemes indicate that the grain boundaries of the metal will not cross from one side to the other. This crossing reduces the resistance of the connection and should improve its reliability. Researchers from Tohoku University in Japan have reported a new metallurgical scheme that can ultimately generate large single crystal copper that crosses boundaries. This is a huge change, "said Takafumi Fukushima, associate professor at Northeastern University. We are currently analyzing the reasons behind it

Other experiments focus on simplifying the mixed bonding process. Some experiments attempt to lower the annealing temperature required to form bonds (typically around 300 ° C), with the motivation of reducing the risk of damage to the chip caused by prolonged heating. Researchers from Applied Materials have introduced the progress of a method that can significantly shorten annealing time - from a few hours to just 5 minutes.

Chip on wafer (CoW) hybrid bonding is currently more useful for the industry: it allows chip manufacturers to stack chips of different sizes together and test each chip before binding it to another, ensuring that they do not cause fatal failures in expensive CPUs due to a single defective component.

But CoW has all the difficulties of WoW, and there are few options to alleviate the difficulties. For example, CMP aims to flatten wafers rather than individual chips. Once the chip is cut from the source wafer and tested, it is difficult to further improve its bonding readiness.

However, Intel reported a CoW hybrid bonding spacing of 3 microns, while Imec achieved 2 microns, mainly by making the transferred chips very flat while still attached to the wafer and keeping them particularly clean during subsequent processes. Both teams' efforts use plasma etching to cut chips, rather than the conventional method of using specialized blades. Plasma will not cause edge fragmentation, resulting in debris that interferes with the connection. It also allows the Imec team to shape chips and create chamfers to reduce mechanical stress that may damage connections.

Multiple researchers have told IEEE Spectrum that CoW hybrid bonding is crucial for the future of high bandwidth memory (HBM). HBM is a DRAM chip stack on top of the control logic chip, currently with a height of 8 to 12 chips. HBM is usually packaged in the same package as high-end GPUs, which is crucial for providing the massive data required to run large language models such as ChatGPT. Nowadays, HBM chips are stacked using the so-called micro bump technology, where tiny solder balls between each layer are surrounded by organic fillers.

But as artificial intelligence further drives memory demand, DRAM manufacturers hope to implement 20 or more layers in HBM chips. However, the volume occupied by micro bumps means that these stacks will soon become too high to be packaged with GPUs. Hybrid bonding not only reduces the height of HBM, but also makes it easier to dissipate excess heat in the package, as the thermal resistance between its layers is smaller.

At ECTC, Samsung engineers demonstrated a hybrid bonding scheme that can produce a 16 layer HBM stack. I think using this technology can create stacks with over 20 layers, "said Hyeonmin Lee, a senior engineer at Samsung

Other new CoW technologies may help introduce hybrid bonding into high bandwidth memory. Souriau stated that although the researchers at CEA Leti did not showcase their research in this area at ECTC, they are currently studying so-called self alignment techniques. This will help ensure CoW connectivity through chemical processes. Some parts of each surface will become hydrophobic, while others will become hydrophilic, allowing the surface to automatically slide into place.

At ECTC, researchers from Tohoku University and Yamaha Robotics reported a study on a similar approach, using the surface tension of water to align 5-micron pads on experimental DRAM chips with an accuracy better than 50 nanometers.

Researchers will almost certainly continue to push for the spacing of hybrid bonding connections. TSMC System Exploration Project Manager Han Jong Chia told ECTC engineers that a 200 nanometer WoW spacing is not only possible, but also desirable. TSMC plans to launch a technology called backside power supply within two years. Intel plans to launch this technology by the end of this year. This technology places the coarse power interconnects of the chip beneath the silicon wafer rather than above it. TSMC researchers have calculated that with these, the topmost interconnect layer can better connect to smaller hybrid bonding pads. The use of backside power supply with 200 nanometer bonding pads will significantly reduce the capacitance of 3D connections, resulting in a product of energy efficiency and signal delay that is nine times greater than that achievable with 400 nanometer bonding pads.

Chia suggests that at some point in the future, if the key spacing is further reduced, it may become feasible to "fold" the circuit block so that it can be built across two wafers. In this way, some longer connections within the block may be shortened through vertical paths, which may accelerate computation speed and reduce power consumption.

Moreover, mixed bonding may not be limited to silicon. CEA Leti's Souriau stated, "Significant progress has been made in the development of silicon to silicon wafers, but we are also seeking hybrid bonding between gallium nitride and silicon wafers, as well as glass wafers... everything is above everything else." His organization even introduced research on hybrid bonding of quantum computing chips, which involves aligning and bonding superconducting niobium instead of copper.

It's hard to say where the limit is, "Souriau said," things are moving too fast

Reference link https://spectrum.ieee.org/hybrid-bonding

Disclaimer: This article is reproduced or adapted online, and the copyright belongs to the original author. The content of the article is the author's personal opinion. Reproduction is only intended to convey a different viewpoint and does not represent the company's endorsement or support of that viewpoint. If you have any objections, please feel free to contact us.